二維電子元件的發展可否成為下一世代的希望 ?!

- 物理專文

- 撰文者:林彥甫 (中興大學物理系)

- 發文日期:2019-04-18

- 點閱次數:3269

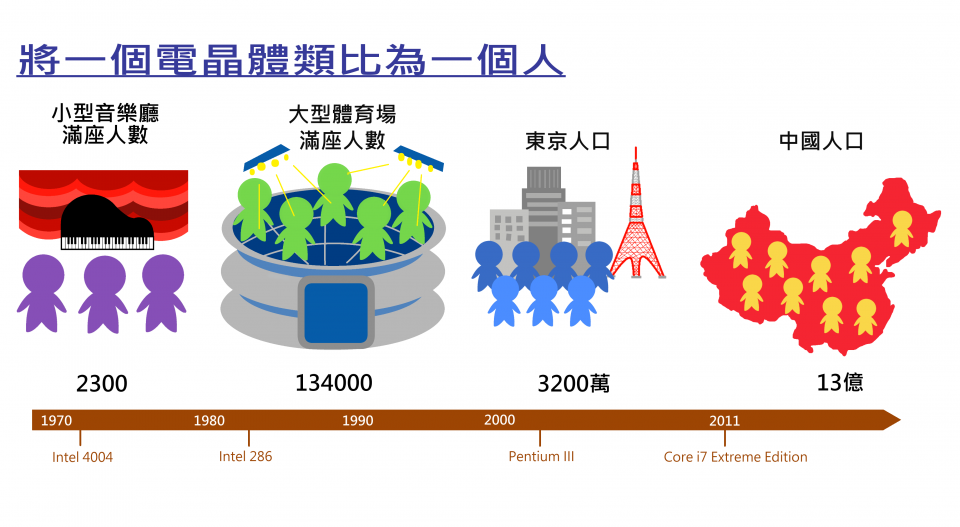

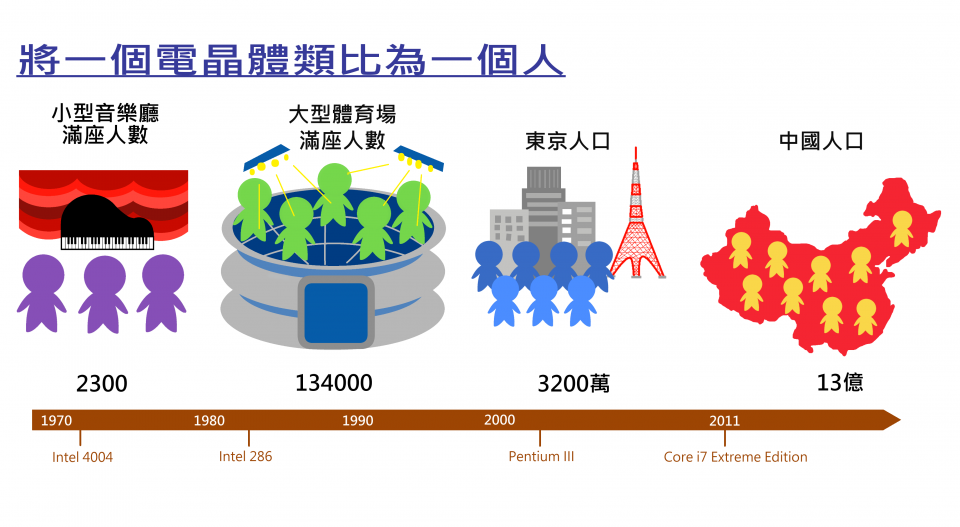

I. 積體電路發展的過去與現在:

1958 年 9 月 12 日,美國德州儀器公司 (Texas Instruments) 的 Jack Kilby 演示了一種工作積體電路 (Integrated Circuits, ICs) 的新穎概念,該積體電路是屬於一種相移振盪器,是使用由單片鍺 (Ge) 元素所製作而成的電晶體 (transistor)、電阻器和電容器元件所構成,並借助『外部』細小的金線將該元件連接到所使用的電路中 [1]。數個月後,於 Fairchild Semiconductor 工作的 Robert Noyce 提出了一種單片積體電路的『概念』,該積體電路的設計基於一平面化的架構,使用矽 (Si) 元素與鋁導線,並將其共同沉積於具有二氧化矽絕緣層的矽晶圓表面,透過鋁導線的嫁接連接數個不同電路元件 [2]。時隔兩年,這樣的共平面積體電路設計的概念,於 1960 年由 Fairchild Semiconductor 公司的工程師團隊將其具體實現,至此,電子元件的連接由以往的各個導線相連而達成工作目標,發展至同一塊基板材料上實現其積體電路功能。1968 年 7 月份,Robert Noyce 更和其合作夥伴以整合式電子元件 (Integrated Electronics) 為名,創建全球最大的半導體積體電路公司:英特爾 (Intel)。1970 年代,該公司所推出的第一款積體電路單元,將 2300 個電晶體製作於12 mm2 基板上。若將一個電晶體類比為一個人,當時積 體電路中電晶體的密度概念,就如同一座小型音樂廳擠入滿堂的人潮一般 ( 如圖 1 左側圖所示 );六十年後的當代,這樣積體電路的概念,已經能將超過13億 (1.3 billion) 個電晶體微縮製造於十倍大的基板上 (122 mm2),這巨幅演進的過程如同將全中國大陸的人口,擠入十座1970 年代的小型音樂廳一般 ( 如圖 1 中右側所示 )。

圖 1: 過去六十年發展過程中,若將電晶體的大小類比於人的體積,1970 年代時,元件中電晶體的密度,如圖小型音樂廳擠入了 2300位觀眾一般,到了 2011 年時,元件中電晶體封裝密度已經可以將全中國的人口塞入十倍大的音樂廳中,這樣誇張的演變見證了電晶體體積微縮化的過程,也具體地說明了 Moore 定律的發展。

時至今日,1958 年夏天 Jack Kilby 首次驗證積體電路概念以來的六十年間,積體電路的爆發性進展已令人感到震驚,該成就後續不但推動了太空時代的來臨、更使得行動通訊、人工智能進入你、我的日常生活中,成為人與人間不可或缺的一環。

半導體積體電路發展至今,其複雜程度早已遠遠超過六十年前科學家們的假設,1969 年 Simon Min Sze 出版全球最著名的半導體元件聖經一書『Physics of Semiconductor Devices』時,也未曾料想到積體電路可以微縮到目前的範疇,Simon Min Sze 新書發表的當下也僅認為微米尺度的電晶體微縮化,大概就是這個領域的邊界了吧。但隨著晶片縮小化過程,所導致的複雜度與成本的驟升,2018 年初英特爾於製造 10 奈米核心技術上,遇到良率大幅下降等嚴重問題,導致大規模量產時程延宕至 2019 年初;另一方面,著名的半導體廠 Global Foundries 也於近期宣布停止開發 7 奈米核心晶片技術 ( 一般相信 Global Foundries 的 7 奈米技術與英特爾 10 奈米技術相當 ),這些原因都歸咎於微縮過程,在矽晶片為主的互補式金屬 - 氧化物 - 半導體場效電晶體 (metal-oxide-semiconductor field-effect transistors, MOSTFETs) 技術變得越來越困難所致。

II. 現代電子元件微縮化所遇到的困難:

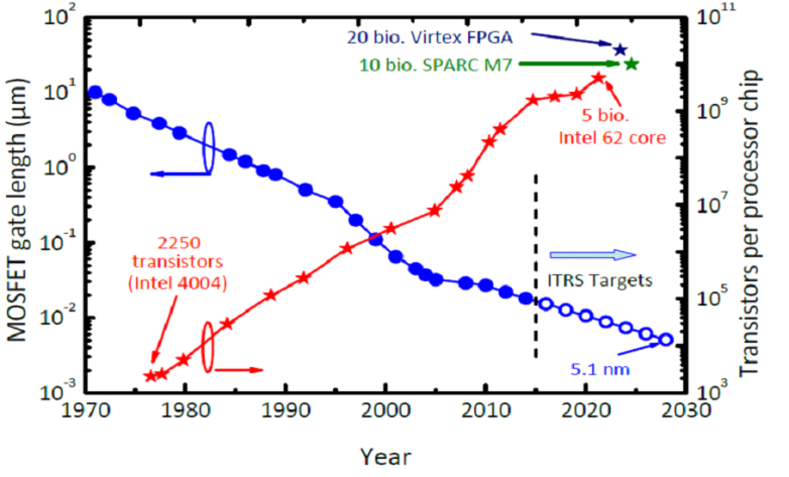

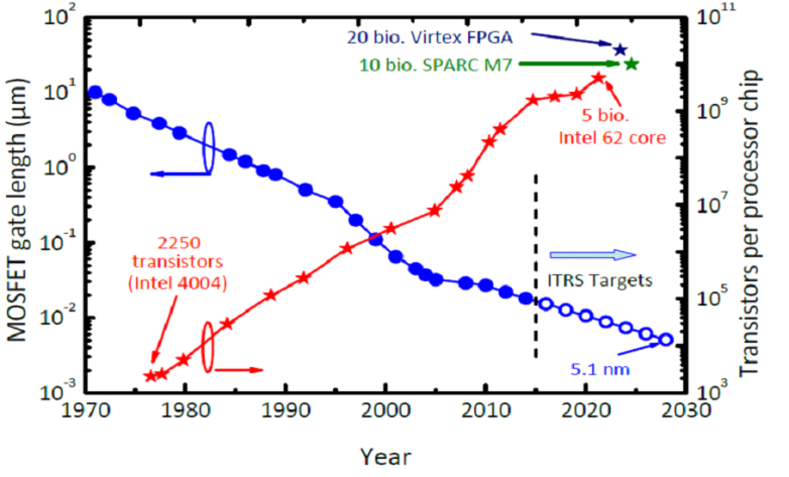

事實上,成熟發展的 MOSFETs 被視為當今積體電路工業蓬勃的主要原因。高速運算元件的建構、儲存晶片的開發與各式微機電通訊的演算皆需以該電晶體為發展基礎的單元。過去四十年,隨著微影技術 (lithography technology) 的精進,為了提高電晶體操作速度與節省所需能源的耗損,單位面積所能夠擁有的電晶體數量不斷地攀升,以重量 0.5 克重、32 GB 的現代化數位記憶體元件為例,其包含的電晶體數目已經高達兩仟億 (> 256 billion MOSFETs) 個之多,這樣難以計數的數量就如同天際銀河系中恆星數的多寡。然而,逐步增加單位面積電晶體的數量的同時,MOSFETs 體積的快速遞減也伴隨而生,圖 2 為電晶體元件尺寸與其單位面積密度隨著時間軸之發展關係,圖中我們可以清楚地觀察到,過去數十年間,半導體電晶體尺寸大小快速地由1960 年代的微米維度,縮減至 2015 年約 5~10 奈米的數量級,此尺寸大小僅為常用半導體材料 - 矽原子間距的十至二十倍。電晶體通道長度並不可能無限制的縮減,當其長度縮小至某個數量級後 ( 約數個奈米長 ),各種因通道長度變小所衍生的問題便會開始發生,導致電晶體效能驟降,並伴隨著嚴重的漏電流現象(current leakage)、臨界偏壓 (threshold voltage) 隨溝道長度降低而遞減、臨界擺幅 (subthreshold swing) 則隨之遞增,此外,載流子表面散射現象、速度飽和趨勢與熱電子效應增加等隨之而生,此類現象我們統稱為元件的短溝道效應 (short-channel effect)。

圖2: 電晶體元件尺寸與其單位面積密度隨著時間軸之發展關係[3]。

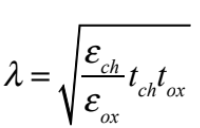

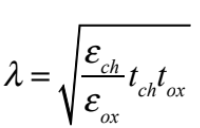

為了克服元件的短溝道效應所帶來的負面影響,放棄傳統平面設計的電晶體結構,將閘極電極 (gate electrode)改為捲繞於導電通道四周圍的方式,藉以改善靜電控制通道的能力,成為目前業界所採取的主要方法之一;另一方面, 若進一步地依據電晶體幾何結構,思考其本徵系統之物理量值,於平面電晶體結構中,表徵短溝道效應的特徵長度 (characteristic length; λ ) 可以使用 來表示其中 εch、εox 、tch 與 tox 分別為半導體通道介電常數、閘極氧化層介電常數、半導體通道厚度與閘極氧化層絕電厚度 [4, 5]。如果以厚度為 5 奈米厚之半導體材料為例,當閘極氧化層為 6 奈米厚二氧化鉿絕緣體,則短溝道效應的特徵長度 λ 僅為 2 奈米,遠遠少於圖 2 顯示目前所遇到短溝道效應之技術瓶頸。

來表示其中 εch、εox 、tch 與 tox 分別為半導體通道介電常數、閘極氧化層介電常數、半導體通道厚度與閘極氧化層絕電厚度 [4, 5]。如果以厚度為 5 奈米厚之半導體材料為例,當閘極氧化層為 6 奈米厚二氧化鉿絕緣體,則短溝道效應的特徵長度 λ 僅為 2 奈米,遠遠少於圖 2 顯示目前所遇到短溝道效應之技術瓶頸。

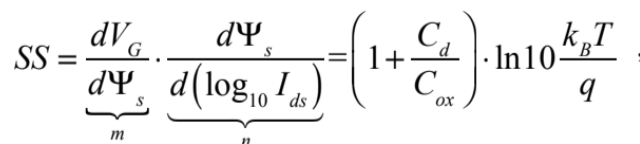

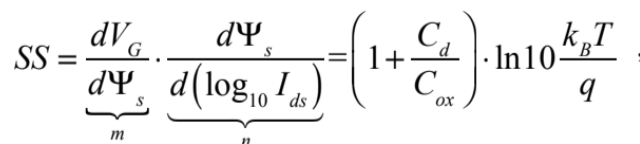

除了電晶體微小化過程所遇到的短溝道效應外,在 MOSFETs 中,由於傳統電流開 /關的過程牽涉到熱載流子注入 (thermal carrier injections) 跨越電位能障礙的機制 [6, 7],基於這樣的操作型定義,限制了整體電晶體開、關速度的快慢與電流比的大小 (switch currenton-off ratio)。科學家定義改變源極 - 汲極電流 (source-drain current, Ids) 一個數量級,所需要施加多少閘極偏壓的物理量,稱為次臨界擺幅 (subthreshold swing, SS),該量值的大小可以表示為

,

,

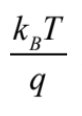

式中 為熱電壓大小 (thermalbvoltage)、 與分別表示通道空乏區與電晶體氧化層電容大小。式中 m 更進一步地表示電晶體本徵因子, n 表示電晶體表面電位 (surface potential) 隨閘極偏壓彎曲程度之大小。

為熱電壓大小 (thermalbvoltage)、 與分別表示通道空乏區與電晶體氧化層電容大小。式中 m 更進一步地表示電晶體本徵因子, n 表示電晶體表面電位 (surface potential) 隨閘極偏壓彎曲程度之大小。

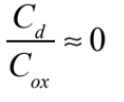

依據熱載流子傳輸機制並忽略電容比值變化的大小,即 。

。

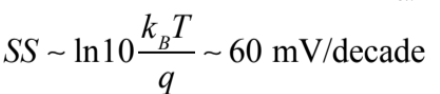

理想狀況下,室溫 MOSFETs最小次臨界擺幅數值約為 ,此物理量意味著當源極 - 汲極電流每上升一個數量極,最少需要付出 60 mV 的驅動電壓。

,此物理量意味著當源極 - 汲極電流每上升一個數量極,最少需要付出 60 mV 的驅動電壓。

隨著單位面積電晶體數目的不斷增加,通道長度不斷地遞減,為了有效的縮小次臨界擺幅的大小並提升電晶體操作效能,新物理系統的探索是迫切需要的。

當今科技發展必須不斷推演,大量數據的快速計算與處理儼然成為趨勢,尋找超越矽以外的戰略性系統或材料,對於創造下一世代設備與繼續發展積體電路是至關重要的。有鑑於此,1990 年代開始的一系列奈米尺度材料開發,為新世代的半導體器件帶來新一番的氣象,碳奈米管或是一維奈米半導體材料的使用,率先被認為是主要潛力主軸之一 [8];另一個相關競爭者是 2004 年由石墨烯 (graphene) 研究開啟的二維片狀材料世代 [9],以及其二維的垂直疊系統 ( 亦或稱為凡德瓦爾異質結構的材料 [10, 11]),這些材料已被用於構建一系列有前景的元件與基本電路,乃至微處理器等功能 [12],筆者將在下面的篇幅中,將針對二維材料於電子元件上的發展做一簡單的描述,希望能引起讀者對於該議題的強烈目光。

III. 二維材料的發展背景與其重要性:

近年來二維層狀材料研究的快速崛起,除提供科學家探索新穎光、電特性之低維度平台外,更實際地給予跨越元件小尺寸下短溝道效應障礙的實質方法。二維材料中除了最廣為人知,但卻缺乏能隙的類金屬石墨烯系統外【註:石墨烯由於不具本徵能隙的特徵,造成邏輯電路元件開發的困難】,具有能帶寬度 (energy bandgap) 的過鍍金屬硫族化合物(transition metal dichalcogenides, TMDs) 是另一受到注目的層狀結構材料,其種類以 Mo 和W 兩大系列為主,搭配 S、Se 與 Te 組合而成 [13],這些材料由於層 - 層間具有與石墨烯相同的凡德瓦力鍵結 (van der Waals force),因此皆可經由物理性膠帶撕貼的方式得到片狀二維奈米結構,此外,由於量子侷限效應的影響,這些過鍍金屬硫族化合物在多層數時,呈現間接能隙 (indirect bandgap) 之半導體特性;但隨著層數遞減,材料能帶寬度逐步擴大,最終體系於單層時轉為直接能隙 (direct bandgap) 半導體,因此,具直接能隙之單層過鍍金屬硫族化合物被預測擁有較佳的光 - 電轉換特性 [14]。第一篇關於單層 TMDs 電晶體的研究於 2011 年發表頂尖奈米期刊 Nature Nanotechnology,內容描述關於單層 MoS2 雙閘極場效應的報導 [15]。這樣一個保有石墨烯二維層狀材料結構的特徵,並具備可調控能帶間隙的半導體二維奈米材料,被視為下一世代發展光 - 電轉換元件重要的系統。

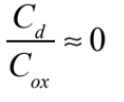

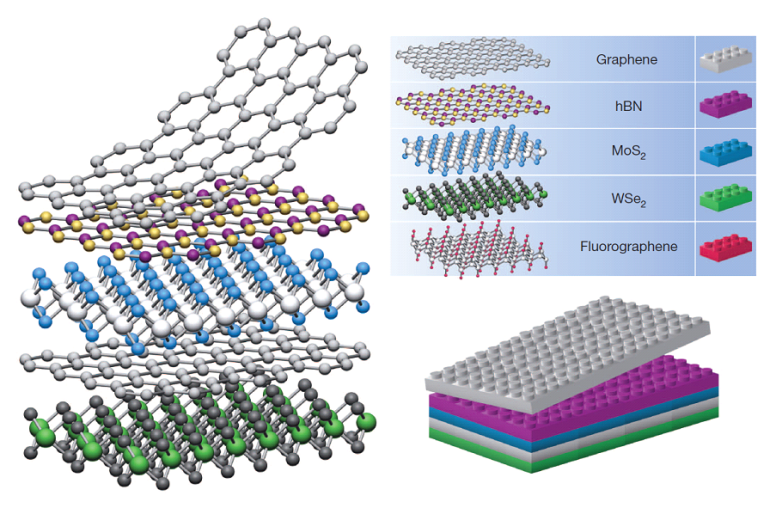

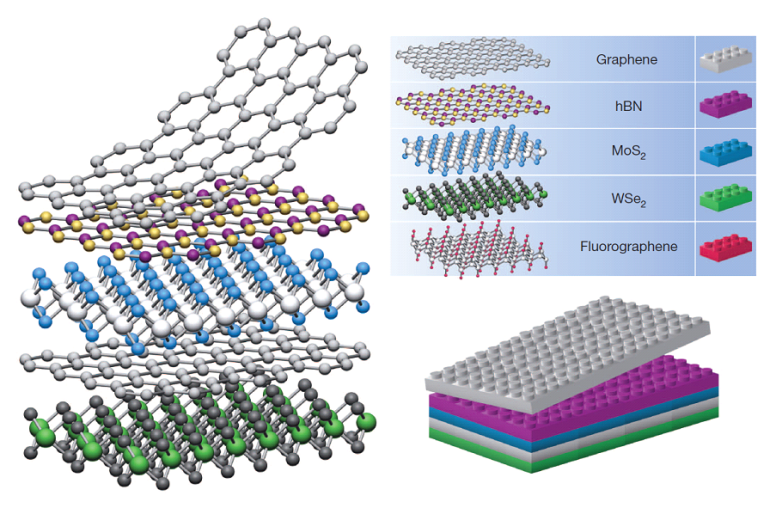

層狀材料種類非常多元,粗估超過百餘樣之多[16],簡單依據電學特徵/能隙結構區分,可以大致區分為金屬性、半導體性、絕緣體性與超導特性,因此,選擇適當的材料作為搭建系統的基石,就能實現任何使用者所需要的功能,甚至多功能積體電路之開發。有別於傳統半導體異質界面系統,界面與界面間原子藉由共價鍵相互接合,二維層狀異質接觸面靠的則是無懸鍵存在的凡德瓦力相互結合,這樣一個藉由凡德瓦力所組成的界面,不僅大幅度地降低傳統異質界面晶格匹配的問題 (lattice mismatch),同時也改善奈米尺度下微觀界面狀態密度消散等問題,因此特別適合用於低維度電子元件系統的建構與開發。具原子級平坦的二維層狀材料被視為是後石墨烯時代凝聚態物理領域重要且開創性的研究主軸之一,二維材料的種類眾多,其平行 / 垂直方向異質結構的堆疊總類更是前所未見,這些二維材料就如同是原子級尺度平整的積木一般,藉由二維砌塊的積累將能夠使得此低維度材料建構出新穎、多元的三維器件,如圖 3 所示。

圖 3: 二維層狀電子系統其建構概念如同堆疊積木一般,層層往上堆疊建構新型、突破短溝道效應之三維電子元件系統 [11]

以凡德瓦力作為層 - 層垂直堆疊的二維奈米系統,最早實現的概念是為了要克服單層石墨烯因為二氧化矽 (SiO2) 表面懸浮鍵所造成的界面傳輸問題。2010 年紐約哥倫比亞大學 C. D. Dean 等人首先將單層石墨烯放置於六角堆積二維氮化硼 (h-BN) 基板,這樣的研究成果大幅的屏除掉二氧化矽基板上電子 - 電洞不均勻分布的漲落問題,並且得到極高的載子遷移率值 [17],此成果除增進了二維材料本徵的元件效能外,在電學與光學上之新興功能性應用也伴隨而生。以物理性機械撕貼法所製作的垂直堆疊二維層狀奈米系統,大致可以分成濕式與乾式兩種轉印法,差別在於撕貼所得之二維層狀奈米材料在製作垂直堆疊系統中,表面是否有與液態溶液相接觸 [18]。截至目前為止,新穎垂直堆疊二維層狀奈米系統從早期以石墨烯堆疊的體系 [19-25],進展到互補式半導體堆疊的層狀平行與垂直異質結構體隙 [26-33],變化之多元與廣泛開創了新形態的研究方向。當今積體電路發展上所遇到的短溝道效應與節能等問題,正可以藉由僅數奈米厚的二維層狀奈米系統的研究與開發,有效地克服所遇到的困難。

IV. 二維電子元件的潛力:

筆者從事低維度電子元件的探索已有數年之久,有鑑於二維層狀材料原子極薄膜厚度對於解決當今電晶體短溝道效應的助益與其優秀的光、電特徵,過去幾年將研究重心著重於二維電子元件的探索與開發上,2014 年開始筆者研究團隊做了一系列關於二維 MoTe2電子元件的報導,這是全球第一個關於該二維材料電子元件的探索,我們的研究團隊由基礎電性做出發到可能感測元件及邏輯電路的實現,筆者希望透過這個簡單的例子,引領讀者對二維電子元件基礎研究的興趣,並進而期待為相關的產業的升級注入新血。

在最廣為人知的二維層狀半導體研究上,2014 年前 MoS2、MoSe2、WS2 與 WSe2 等相關電子元件研究先後地被報導,其電學特性展現了良好的單極性開、關特徵,並且凸顯出了有效解決短溝道效應的契機,當年在對於 TMDs 系列的研究過程中,關於 Te 二維層狀複合物的研究報導一直是一片未開發的藍海。事實上,關於 TMDs 塊材的合成技術早已開發四、五十年以上,相關的細節早已在 1977 年出版的『Preparation and crystal growth of materials with layered structures』書中詳載 [34],MoS2 塊材更是廣為人們使用的固體潤滑劑材料之一,但一直到了 2004 年石墨烯研究的進展,才重新開啟了開學家對於層狀材料的注目。筆者的研究團隊於 2013 年領先世界成為全球第一個探索二維 MoTe2 電子元件的研究群。結構上 MoTe2 材料是由上、下雙層 Te 原子以三明治結構方式夾擊 Mo 原子所形成之穩定系統,此外,由於 Te 原子相對於 Mo 原子鍵結轉角上的差異,其電學特徵又可區分為金屬性 (β 態 ) 與半導體性 (α 態 ),為了研究該材料對於電晶體與積體電路發展的潛力,因此筆者研究團隊僅專注於半導體性的 MoTe2 電子元件探索。α 態的 MoTe2 塊材具有1 eV 能隙大小的非直接半導體材料,隨著厚度由塊材降低至單層,其能隙大小變化不大,但會由非直接能隙轉為直接能隙半導體,有利於光電能量的轉換,這樣一個與傳統 Si 元素相近的能隙大小,相較於其他 TMDs 材料預期將有著更好的光吸收特徵。此外,在理論的預測 MoTe2 具有高的載子遷移率,使得快速二維電子元件的開發變的可行。不同載子極性的塊材研究成果也已經在 20 多年前被報導,用來實現基礎積體電路元件的 p-n 二極體。有鑑於此,筆者的研究團隊,利用化學氣相傳輸 (Chemical Vapor Transport) 的方式,實現 α 態的 MoTe2 塊材的合成,並且率先採用物理性膠帶撕貼技術完成全球首個二維層狀MoTe2 電子元件的製作與電學探索 [35]。

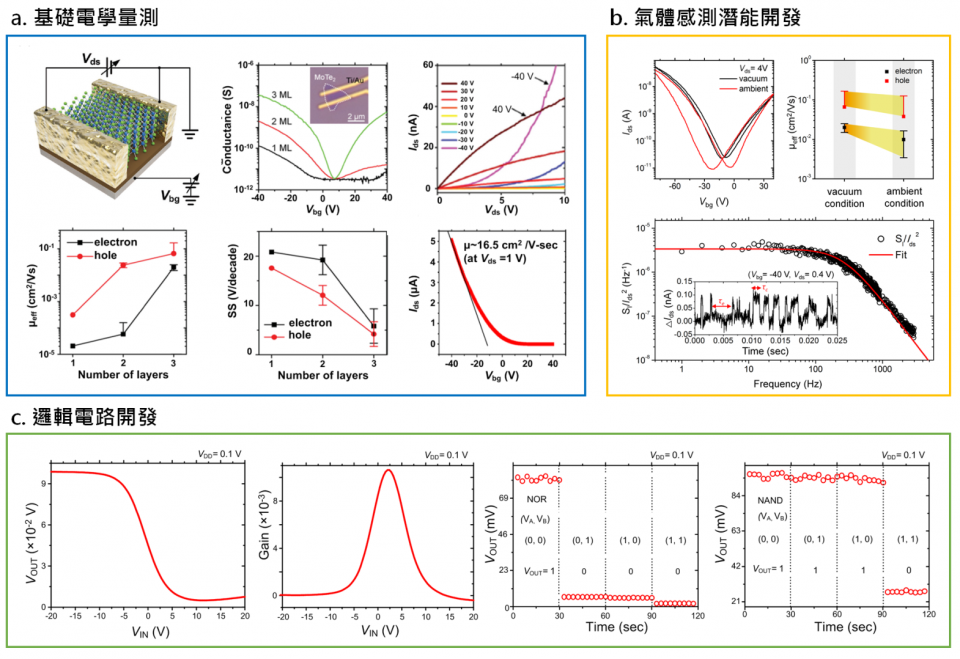

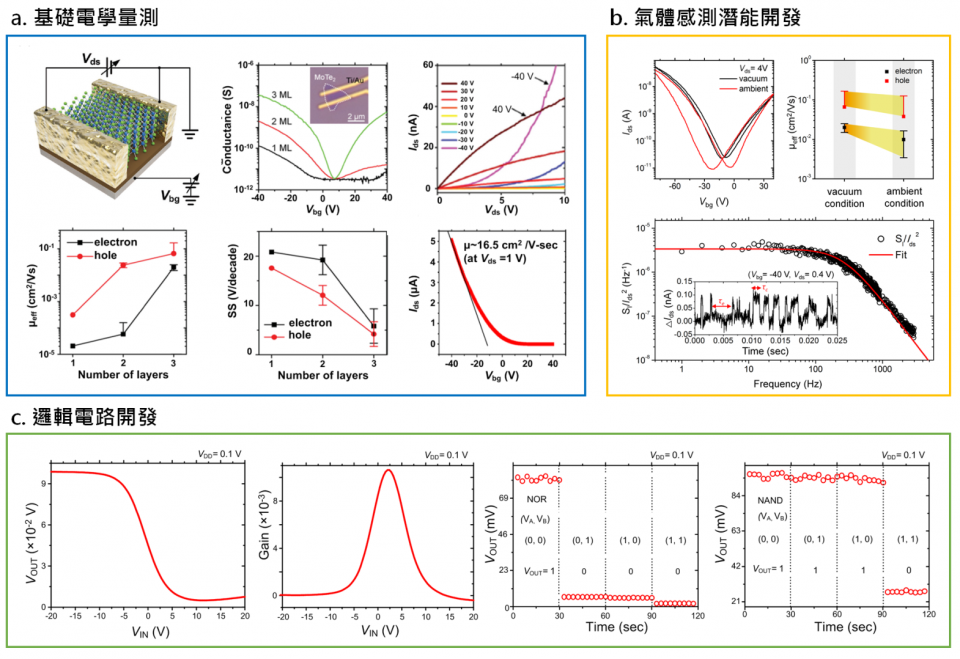

圖 4: 二維層狀 MoTe2 電晶體,a. 基礎電學量測、b. 氣體感測潛能開發、c. 邏輯電路開發 [35-38]。

圖 4 中筆者將過去五年關於研究二維 MoTe2 電子元件的具體成果簡單摘錄。2014 年春天,筆者研究團隊首先驗證了單層 MoTe2 材料能夠透過物理性手段,成功的鋪放於器件基板上,透過這件事情的驗證,我們揭露了單層至多層 MoTe2 電晶體的基本電學特徵 ( 如圖 4a 所示 ),這項工作中,MoTe2 展現了非典型的單極性電流 - 電壓轉換特徵,透過閘極正、負電壓的施加,該層狀電子元件無論單層或是多層皆呈現雙極性的傳輸特徵 ( 即單一電晶體簡單地透過電場的操作,就可以表現出電子或電洞主導的特徵 ),這樣特異型的表現使得積體電路的設計能變得更加簡便,並預期能夠實現更高元件密度堆疊的可能性。此外,透過不同金屬電極的替換,該二維層狀電子元件的載子遷移率變得可以操控,並且表徵出 10-3~102cm2/V-sec 範疇的大小,該載子遷移率的範圍雖然小於當今對商業產品的最低要求,但其僅透過置換電極材料而非元素摻雜手段,達成可調控的載子遷移率,著實為二維電子元件工程的改善,提供一條新穎的方法。二維材料具備了大的表面對體積比例,因此電子元件受到環境氛圍影響特別明顯,筆者藉由這樣的特徵進一步的觀察到,可以透過二維 MoTe2 電晶體的交流電學量測,實現微小訊號環境感測器的功能,如圖 4b 所示。另一方面,因二維材料具有極薄的器件通道厚度,雖可以有效克服短溝道效應的影響,但也因為先天性地限制了傳統半導體工藝「電子 / 電洞摻雜手段的施行」,因此思考如何有效地控制層狀 MoTe2 電子元件的載子濃度,進而改變電學特徵,實現省電的邏輯電路,一直是發展二維層狀電晶體應用上重要的探討議題。筆者基於對於二維層狀 MoTe2 電晶體基礎電學機制的深刻認知,進一步地開發了一個全新電子 / 電洞可操控、反覆式摻雜手法,並稱此為 Electrothermal Doping Processes。筆者團隊透過真空下施加一高電場於二維層狀MoTe2 通道上的手段,實現了元件電子的摻雜;另一方面,將電子摻雜後的二維電晶體曝氣於大氣環境中,這樣電子摻雜的元件會被進一步地反轉為電洞摻雜;這些電子 / 電洞摻雜過程歸因於二維材料表面與水 / 氧分子結合所致 ( 即高靈敏環境感測因素所致 )。該工作中,筆者除了能精密調控兩種載子極性電晶體外,更實現了積體電路中的反向器、反或閘(not or gate, NOR gate) 與反及閘 (not and gate, NAND gate) 等重要且基礎的元件功能,如圖4c 所示。

V. 結語與展望:

『半導體』、『二維』材料電子元件的發展,可以粗略地由 2011 年瑞士 A. Kis 團隊於頂尖奈米期刊 Nature Nanotechnology 發表單層 MoS2 電晶體開始界定起,時至今日該領域的探索爆量發展,筆者對於二維電子元件的研究與理解也僅是冰山一角,就筆者角度而言,距離使用二維電子元件,乃至發展積體電路並進入日常,尚有一段非常長的研究道路。

“The World is Flat: A Brief History of the Twenty-First Century is an international best-selling book by Thomas Friedman that analyzes globalization in the early 21st century. The title, perhaps modified to The world is 2D, is also appropriate for science in the 21st century, as exemplified by the recent interest in graphene and other two-dimensional (2D) materials” [39],這是一段摘錄於 2013 年 7 月頂級奈米領域期刊 ACS Nano 第七期第七卷第一頁雜誌中,編輯者引言所使用的開場白,說明了石墨烯與其相關二維材料的研究在近年所受到的高度重視;西元前三百三十年,古希臘哲學家亞里斯多德發現越往北走,北極星離地面漸高,而越往南行,卻看到北極星離地面越低,因此,根據經驗法則,他提出大地是球體的概念,然而這樣打破傳統思維的想法卻一直受到擁護大地平面說學者的批判,直到西元後一千五百年才由哥倫布證實大地球體說的正確性;2004 年證實石墨烯存在後,二十一世紀的科學家或工程師又將精力再次集中於這讓人熱血沸騰的二維世界中,筆者希望透過雙月刊這短短的物理專文撰寫機會,激發讀者內心對該領域未知探索的渴望,更進而參與其中、樂在其中。

參考資料:

1. J. Kilby, IEEE Trans. of Electron Devices 23, 648 (1976).

2. C. H. Museum, https://go.nature.com/2wF9Q1r (2018).

3. F. Schwierz, J. Pezoldt and R. Granzner, Nanoscale 7, 8261 (2015).

4. R. H. Yan, A. Ourmazd and K. F. Lee, IEEE Trans. Electron Devices 39, 1704 (1992).

5. H. Liu, A. T. Neal and P. D. Ye, ACS Nano 6, 8563 (2012).

6. S. M. Sze, Physics of Semiconductor Devices 1st edn., John Wiley (1969).

7. M. S. Lundstrom, Proc. IEEE Int. SOI Conf. 1-3 (2006).

8. P. L. McEuen, Nature 393, 15 (1998).

9. K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva and A. A. Firsov, Science 306, 666 (2004).

10. K. S. Novoselov and A. H. Castro Neto, Phys. Scr. T146, 014006 (2012).

11. A. K. Geim and I. V. Grigorieva, Nature 499, 419 (2013).

12. S. Wachter, D. K. Polyushkin, O. Bethge and T. Mueller, Nat. Commun. 8, 14948 (2017).

13. M. Chhowalla, H. S. Shin, G. Eda, L. J. Li, K. P. Loh, and H. Zhang, Nat. Chem. 5, 263 (2013).

14. H. Schmidt, F. Giustiniano, and G. Eda, Chem. Soc. Rev. 44, 7715 (2015).

15. B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti and A. Kis, Nat. Nanotechnol. 6, 147 (2011).

16. F. Wang, Z. Wang, C. Jiang, L. Yin, R. Cheng, X. Zhan, K. Xu, F. Wang, Y. Zhang, and J. He, small 13, 1604298 (2017).

17. C. R. Dean, A. F. Young, I. Meric, C. Lee, L. Wang, S. Sorgenfrei, K. Watanabe, T. Taniguchi, P. Kim, K. L. Shepard and J. Hone, Nat. Nanotehnol. 5, 722 (2010).

18. A. C. Ferrari, F. Bonaccorso, V. Fal'ko, K. S. Novoselov, S. Roche, P. Boggild, S. Borini, F. H. Koppens, V. Palermo, N. Pugno, J. A. Garrido, R. Sordan, A. Bianco, L. Ballerini, M. Prato, E. Lidorikis, J. Kivioja, C. Marinelli, T. Ryhanen, A. Morpurgo, J. N. Coleman,V. Nicolosi, L. Colombo, A. Fert, M. Garcia-Hernandez, A. Bachtold, G. F. Schneider, F. Guinea, C. Dekker, M. Barbone, Z. Sun, C. Galiotis, A. N. Grigorenko, G. Konstantatos, A. Kis, M. Katsnelson, L. Vandersypen, A. Loiseau, V. Morandi, D. Neumaier, E. Treossi, V.

Pellegrini, M. Polini, A. Tredicucci, G. M. Williams, B. H. Hong, J. H. Ahn, J. M. Kim, H. Zirath, B. J. van Wees, H. van der Zant, L. Occhipinti, A. Di Matteo, I. A. Kinloch, T. Seyller, E. Quesnel, X. Feng, K. Teo, N. Rupesinghe, P. Hakonen, S. R. Neil, Q. Tannock, T. Lofwander and J. Kinaret, Nanoscale 7, 4598 (2015).

19. K. Roy, M. Padmanabhan, S. Goswami, T. P. Sai, G. Ramalingam, S. Raghavan and A Ghosh, Nat. Nanotechnol. 8, 826 (2013).

20. T. Georgiou, R. Jalil, B. D. Belle, L. Britnell, R. V. Gorbachev, S. V. Morozov, Y. J. Kim, A. Gholinia, S. J. Haigh, O. Makarovsky, L. Eaves, L. A. Ponomarenko, A. K. Geim, K. S. Novoselov and A. Mishchenko, Nat. Nanotechnol. 8, 100 (2013).

21. W. J. Yu, Z. Li, H. Zhou, Y. Chen, Y. Wang, Y. Huang and X. Duan, Nat. Mater. 12, 246 (2013).

22. L. Britnell, R. V. Gorbachev, R. Jalil, B. D. Belle, F. Schedin, A. Mishchenko, T. Georgiou, M. I. Katsnelson, L. Eaves, S. V. Morozov, N. M. R. Peres, J. Leist, A. K. Geim, K. S. Novoselov and L. A. Ponomarenko, Science 335, 947 (2012).

23. M. S. Choi, G. H. Lee, Y. J. Yu, D. Y. Lee, S. H. Lee, P. Kim, J. Hone and W. J. Yoo, Nat. Commun. 4, 1624 (2013).

24. W. J. Yu, Y. Liu, H. Zhou, A. Yin, Z. Li, Y. Huang and X. Duan, Nat. Nanotechnol. 8, 952 (2013).

25. L. Britnell, R. M. Ribeiro, A. Eckmann, R. Jalil, B. D. Belle, A. Mishchenko, Y. J. Kim, R. V. Gorbachev, T. Georgiou, S. V. Morozov, A. N. Grigorenko, A. K. Geim, C. Casiraghi, A. H. C. Neto and K. S. Novoselov, Science 340, 1311 (2013).

26. K. Roy, M. Padmanabhan, S. Goswami, T. P. Sai, G. Ramalingam, S. Raghavan and A Ghosh, Nat. Nanotechnol. 8, 826 (2013).

27. T. Georgiou, R. Jalil, B. D. Belle, L. Britnell, R. V. Gorbachev, S. V. Morozov, Y. J. Kim, A. Gholinia, S. J. Haigh, O. Makarovsky, L. Eaves, L. A. Ponomarenko, A. K. Geim, K. S. Novoselov and A. Mishchenko, Nat. Nanotechnol. 8, 100 (2013).

28. W. J. Yu, Z. Li, H. Zhou, Y. Chen, Y. Wang, Y. Huang and X. Duan, Nat. Mater. 12, 246 (2013).

29. L. Britnell, R. V. Gorbachev, R. Jalil, B. D. Belle, F. Schedin, A. Mishchenko, T. Georgiou, M. I. Katsnelson, L. Eaves, S. V. Morozov, N. M. R. Peres, J. Leist, A. K. Geim, K. S. Novoselov and L. A. Ponomarenko, Science 335, 947 (2012).

30. M. S. Choi, G. H. Lee, Y. J. Yu, D. Y. Lee, S. H. Lee, P. Kim, J. Hone and W. J. Yoo, Nat. Commun. 4, 1624 (2013).

31. W. J. Yu, Y. Liu, H. Zhou, A. Yin, Z. Li, Y. Huang and X. Duan, Nat. Nanotechnol. 8, 952 (2013).

32. L. Britnell, R. M. Ribeiro, A. Eckmann, R. Jalil, B. D. Belle, A. Mishchenko, Y. J. Kim, R. V. Gorbachev, T. Georgiou, S. V. Morozov, A. N. Grigorenko, A. K. Geim, C. Casiraghi, A. H. C. Neto and K. S. Novoselov, Science 340, 1311 (2013).

33. J. Miao, Z. Xu, Q. Li, A. Bowman, S. Zhang, W. Hu, Z. Zhou, and C. Wang, ACS Nano 11, 10472 (2017).

34. R. M. A. Lieth, Preparation and crystal growth of materials with layered structures. Vol.1. Springer (1977).

35. Y. F. Lin, Y. Xu, S. T. Wang, S. L. Li, M. Yamamoto, A. A. Ferreira, W. Li, H. Sun, W. B. Jian, S. Nakaharai, K. Ueno and K. Tsukagoshi, Adv. Mater. 26, 3263 (2014).

36. Y. F. Lin, Y. Xu, C. Y. Lin, Y. W. Suen, M. Yamamoto, S. Nakaharai, K. Ueno, and K. Tsukagoshi, Adv. Mater.

27, 6612 (2015).

37. Y. M. Chang, C. Y. Lin, Y. F. Lin, and K. Tsukagoshi, Jpn. J. Appl. Phys. 55, 1102A1 (2016).

38. Y. M. Chang, S. H. Yang, C. Y. Lin, C. H. Chen, C. H. Lien, W. B. Jian, K. Ueno, Y. W. Suen, K. Tsukagoshi, and Y. F. Lin, Adv. Mater. 30, 1706995 (2018).

39. A. T. S. Wee, ACS Nano 7, 5649 (2013).

1958 年 9 月 12 日,美國德州儀器公司 (Texas Instruments) 的 Jack Kilby 演示了一種工作積體電路 (Integrated Circuits, ICs) 的新穎概念,該積體電路是屬於一種相移振盪器,是使用由單片鍺 (Ge) 元素所製作而成的電晶體 (transistor)、電阻器和電容器元件所構成,並借助『外部』細小的金線將該元件連接到所使用的電路中 [1]。數個月後,於 Fairchild Semiconductor 工作的 Robert Noyce 提出了一種單片積體電路的『概念』,該積體電路的設計基於一平面化的架構,使用矽 (Si) 元素與鋁導線,並將其共同沉積於具有二氧化矽絕緣層的矽晶圓表面,透過鋁導線的嫁接連接數個不同電路元件 [2]。時隔兩年,這樣的共平面積體電路設計的概念,於 1960 年由 Fairchild Semiconductor 公司的工程師團隊將其具體實現,至此,電子元件的連接由以往的各個導線相連而達成工作目標,發展至同一塊基板材料上實現其積體電路功能。1968 年 7 月份,Robert Noyce 更和其合作夥伴以整合式電子元件 (Integrated Electronics) 為名,創建全球最大的半導體積體電路公司:英特爾 (Intel)。1970 年代,該公司所推出的第一款積體電路單元,將 2300 個電晶體製作於12 mm2 基板上。若將一個電晶體類比為一個人,當時積 體電路中電晶體的密度概念,就如同一座小型音樂廳擠入滿堂的人潮一般 ( 如圖 1 左側圖所示 );六十年後的當代,這樣積體電路的概念,已經能將超過13億 (1.3 billion) 個電晶體微縮製造於十倍大的基板上 (122 mm2),這巨幅演進的過程如同將全中國大陸的人口,擠入十座1970 年代的小型音樂廳一般 ( 如圖 1 中右側所示 )。

圖 1: 過去六十年發展過程中,若將電晶體的大小類比於人的體積,1970 年代時,元件中電晶體的密度,如圖小型音樂廳擠入了 2300位觀眾一般,到了 2011 年時,元件中電晶體封裝密度已經可以將全中國的人口塞入十倍大的音樂廳中,這樣誇張的演變見證了電晶體體積微縮化的過程,也具體地說明了 Moore 定律的發展。

時至今日,1958 年夏天 Jack Kilby 首次驗證積體電路概念以來的六十年間,積體電路的爆發性進展已令人感到震驚,該成就後續不但推動了太空時代的來臨、更使得行動通訊、人工智能進入你、我的日常生活中,成為人與人間不可或缺的一環。

半導體積體電路發展至今,其複雜程度早已遠遠超過六十年前科學家們的假設,1969 年 Simon Min Sze 出版全球最著名的半導體元件聖經一書『Physics of Semiconductor Devices』時,也未曾料想到積體電路可以微縮到目前的範疇,Simon Min Sze 新書發表的當下也僅認為微米尺度的電晶體微縮化,大概就是這個領域的邊界了吧。但隨著晶片縮小化過程,所導致的複雜度與成本的驟升,2018 年初英特爾於製造 10 奈米核心技術上,遇到良率大幅下降等嚴重問題,導致大規模量產時程延宕至 2019 年初;另一方面,著名的半導體廠 Global Foundries 也於近期宣布停止開發 7 奈米核心晶片技術 ( 一般相信 Global Foundries 的 7 奈米技術與英特爾 10 奈米技術相當 ),這些原因都歸咎於微縮過程,在矽晶片為主的互補式金屬 - 氧化物 - 半導體場效電晶體 (metal-oxide-semiconductor field-effect transistors, MOSTFETs) 技術變得越來越困難所致。

II. 現代電子元件微縮化所遇到的困難:

事實上,成熟發展的 MOSFETs 被視為當今積體電路工業蓬勃的主要原因。高速運算元件的建構、儲存晶片的開發與各式微機電通訊的演算皆需以該電晶體為發展基礎的單元。過去四十年,隨著微影技術 (lithography technology) 的精進,為了提高電晶體操作速度與節省所需能源的耗損,單位面積所能夠擁有的電晶體數量不斷地攀升,以重量 0.5 克重、32 GB 的現代化數位記憶體元件為例,其包含的電晶體數目已經高達兩仟億 (> 256 billion MOSFETs) 個之多,這樣難以計數的數量就如同天際銀河系中恆星數的多寡。然而,逐步增加單位面積電晶體的數量的同時,MOSFETs 體積的快速遞減也伴隨而生,圖 2 為電晶體元件尺寸與其單位面積密度隨著時間軸之發展關係,圖中我們可以清楚地觀察到,過去數十年間,半導體電晶體尺寸大小快速地由1960 年代的微米維度,縮減至 2015 年約 5~10 奈米的數量級,此尺寸大小僅為常用半導體材料 - 矽原子間距的十至二十倍。電晶體通道長度並不可能無限制的縮減,當其長度縮小至某個數量級後 ( 約數個奈米長 ),各種因通道長度變小所衍生的問題便會開始發生,導致電晶體效能驟降,並伴隨著嚴重的漏電流現象(current leakage)、臨界偏壓 (threshold voltage) 隨溝道長度降低而遞減、臨界擺幅 (subthreshold swing) 則隨之遞增,此外,載流子表面散射現象、速度飽和趨勢與熱電子效應增加等隨之而生,此類現象我們統稱為元件的短溝道效應 (short-channel effect)。

圖2: 電晶體元件尺寸與其單位面積密度隨著時間軸之發展關係[3]。

為了克服元件的短溝道效應所帶來的負面影響,放棄傳統平面設計的電晶體結構,將閘極電極 (gate electrode)改為捲繞於導電通道四周圍的方式,藉以改善靜電控制通道的能力,成為目前業界所採取的主要方法之一;另一方面, 若進一步地依據電晶體幾何結構,思考其本徵系統之物理量值,於平面電晶體結構中,表徵短溝道效應的特徵長度 (characteristic length; λ ) 可以使用

來表示其中 εch、εox 、tch 與 tox 分別為半導體通道介電常數、閘極氧化層介電常數、半導體通道厚度與閘極氧化層絕電厚度 [4, 5]。如果以厚度為 5 奈米厚之半導體材料為例,當閘極氧化層為 6 奈米厚二氧化鉿絕緣體,則短溝道效應的特徵長度 λ 僅為 2 奈米,遠遠少於圖 2 顯示目前所遇到短溝道效應之技術瓶頸。

來表示其中 εch、εox 、tch 與 tox 分別為半導體通道介電常數、閘極氧化層介電常數、半導體通道厚度與閘極氧化層絕電厚度 [4, 5]。如果以厚度為 5 奈米厚之半導體材料為例,當閘極氧化層為 6 奈米厚二氧化鉿絕緣體,則短溝道效應的特徵長度 λ 僅為 2 奈米,遠遠少於圖 2 顯示目前所遇到短溝道效應之技術瓶頸。除了電晶體微小化過程所遇到的短溝道效應外,在 MOSFETs 中,由於傳統電流開 /關的過程牽涉到熱載流子注入 (thermal carrier injections) 跨越電位能障礙的機制 [6, 7],基於這樣的操作型定義,限制了整體電晶體開、關速度的快慢與電流比的大小 (switch currenton-off ratio)。科學家定義改變源極 - 汲極電流 (source-drain current, Ids) 一個數量級,所需要施加多少閘極偏壓的物理量,稱為次臨界擺幅 (subthreshold swing, SS),該量值的大小可以表示為

,

,式中

為熱電壓大小 (thermalbvoltage)、 與分別表示通道空乏區與電晶體氧化層電容大小。式中 m 更進一步地表示電晶體本徵因子, n 表示電晶體表面電位 (surface potential) 隨閘極偏壓彎曲程度之大小。

為熱電壓大小 (thermalbvoltage)、 與分別表示通道空乏區與電晶體氧化層電容大小。式中 m 更進一步地表示電晶體本徵因子, n 表示電晶體表面電位 (surface potential) 隨閘極偏壓彎曲程度之大小。依據熱載流子傳輸機制並忽略電容比值變化的大小,即

。

。理想狀況下,室溫 MOSFETs最小次臨界擺幅數值約為

,此物理量意味著當源極 - 汲極電流每上升一個數量極,最少需要付出 60 mV 的驅動電壓。

,此物理量意味著當源極 - 汲極電流每上升一個數量極,最少需要付出 60 mV 的驅動電壓。隨著單位面積電晶體數目的不斷增加,通道長度不斷地遞減,為了有效的縮小次臨界擺幅的大小並提升電晶體操作效能,新物理系統的探索是迫切需要的。

當今科技發展必須不斷推演,大量數據的快速計算與處理儼然成為趨勢,尋找超越矽以外的戰略性系統或材料,對於創造下一世代設備與繼續發展積體電路是至關重要的。有鑑於此,1990 年代開始的一系列奈米尺度材料開發,為新世代的半導體器件帶來新一番的氣象,碳奈米管或是一維奈米半導體材料的使用,率先被認為是主要潛力主軸之一 [8];另一個相關競爭者是 2004 年由石墨烯 (graphene) 研究開啟的二維片狀材料世代 [9],以及其二維的垂直疊系統 ( 亦或稱為凡德瓦爾異質結構的材料 [10, 11]),這些材料已被用於構建一系列有前景的元件與基本電路,乃至微處理器等功能 [12],筆者將在下面的篇幅中,將針對二維材料於電子元件上的發展做一簡單的描述,希望能引起讀者對於該議題的強烈目光。

III. 二維材料的發展背景與其重要性:

近年來二維層狀材料研究的快速崛起,除提供科學家探索新穎光、電特性之低維度平台外,更實際地給予跨越元件小尺寸下短溝道效應障礙的實質方法。二維材料中除了最廣為人知,但卻缺乏能隙的類金屬石墨烯系統外【註:石墨烯由於不具本徵能隙的特徵,造成邏輯電路元件開發的困難】,具有能帶寬度 (energy bandgap) 的過鍍金屬硫族化合物(transition metal dichalcogenides, TMDs) 是另一受到注目的層狀結構材料,其種類以 Mo 和W 兩大系列為主,搭配 S、Se 與 Te 組合而成 [13],這些材料由於層 - 層間具有與石墨烯相同的凡德瓦力鍵結 (van der Waals force),因此皆可經由物理性膠帶撕貼的方式得到片狀二維奈米結構,此外,由於量子侷限效應的影響,這些過鍍金屬硫族化合物在多層數時,呈現間接能隙 (indirect bandgap) 之半導體特性;但隨著層數遞減,材料能帶寬度逐步擴大,最終體系於單層時轉為直接能隙 (direct bandgap) 半導體,因此,具直接能隙之單層過鍍金屬硫族化合物被預測擁有較佳的光 - 電轉換特性 [14]。第一篇關於單層 TMDs 電晶體的研究於 2011 年發表頂尖奈米期刊 Nature Nanotechnology,內容描述關於單層 MoS2 雙閘極場效應的報導 [15]。這樣一個保有石墨烯二維層狀材料結構的特徵,並具備可調控能帶間隙的半導體二維奈米材料,被視為下一世代發展光 - 電轉換元件重要的系統。

層狀材料種類非常多元,粗估超過百餘樣之多[16],簡單依據電學特徵/能隙結構區分,可以大致區分為金屬性、半導體性、絕緣體性與超導特性,因此,選擇適當的材料作為搭建系統的基石,就能實現任何使用者所需要的功能,甚至多功能積體電路之開發。有別於傳統半導體異質界面系統,界面與界面間原子藉由共價鍵相互接合,二維層狀異質接觸面靠的則是無懸鍵存在的凡德瓦力相互結合,這樣一個藉由凡德瓦力所組成的界面,不僅大幅度地降低傳統異質界面晶格匹配的問題 (lattice mismatch),同時也改善奈米尺度下微觀界面狀態密度消散等問題,因此特別適合用於低維度電子元件系統的建構與開發。具原子級平坦的二維層狀材料被視為是後石墨烯時代凝聚態物理領域重要且開創性的研究主軸之一,二維材料的種類眾多,其平行 / 垂直方向異質結構的堆疊總類更是前所未見,這些二維材料就如同是原子級尺度平整的積木一般,藉由二維砌塊的積累將能夠使得此低維度材料建構出新穎、多元的三維器件,如圖 3 所示。

圖 3: 二維層狀電子系統其建構概念如同堆疊積木一般,層層往上堆疊建構新型、突破短溝道效應之三維電子元件系統 [11]

以凡德瓦力作為層 - 層垂直堆疊的二維奈米系統,最早實現的概念是為了要克服單層石墨烯因為二氧化矽 (SiO2) 表面懸浮鍵所造成的界面傳輸問題。2010 年紐約哥倫比亞大學 C. D. Dean 等人首先將單層石墨烯放置於六角堆積二維氮化硼 (h-BN) 基板,這樣的研究成果大幅的屏除掉二氧化矽基板上電子 - 電洞不均勻分布的漲落問題,並且得到極高的載子遷移率值 [17],此成果除增進了二維材料本徵的元件效能外,在電學與光學上之新興功能性應用也伴隨而生。以物理性機械撕貼法所製作的垂直堆疊二維層狀奈米系統,大致可以分成濕式與乾式兩種轉印法,差別在於撕貼所得之二維層狀奈米材料在製作垂直堆疊系統中,表面是否有與液態溶液相接觸 [18]。截至目前為止,新穎垂直堆疊二維層狀奈米系統從早期以石墨烯堆疊的體系 [19-25],進展到互補式半導體堆疊的層狀平行與垂直異質結構體隙 [26-33],變化之多元與廣泛開創了新形態的研究方向。當今積體電路發展上所遇到的短溝道效應與節能等問題,正可以藉由僅數奈米厚的二維層狀奈米系統的研究與開發,有效地克服所遇到的困難。

IV. 二維電子元件的潛力:

筆者從事低維度電子元件的探索已有數年之久,有鑑於二維層狀材料原子極薄膜厚度對於解決當今電晶體短溝道效應的助益與其優秀的光、電特徵,過去幾年將研究重心著重於二維電子元件的探索與開發上,2014 年開始筆者研究團隊做了一系列關於二維 MoTe2電子元件的報導,這是全球第一個關於該二維材料電子元件的探索,我們的研究團隊由基礎電性做出發到可能感測元件及邏輯電路的實現,筆者希望透過這個簡單的例子,引領讀者對二維電子元件基礎研究的興趣,並進而期待為相關的產業的升級注入新血。

在最廣為人知的二維層狀半導體研究上,2014 年前 MoS2、MoSe2、WS2 與 WSe2 等相關電子元件研究先後地被報導,其電學特性展現了良好的單極性開、關特徵,並且凸顯出了有效解決短溝道效應的契機,當年在對於 TMDs 系列的研究過程中,關於 Te 二維層狀複合物的研究報導一直是一片未開發的藍海。事實上,關於 TMDs 塊材的合成技術早已開發四、五十年以上,相關的細節早已在 1977 年出版的『Preparation and crystal growth of materials with layered structures』書中詳載 [34],MoS2 塊材更是廣為人們使用的固體潤滑劑材料之一,但一直到了 2004 年石墨烯研究的進展,才重新開啟了開學家對於層狀材料的注目。筆者的研究團隊於 2013 年領先世界成為全球第一個探索二維 MoTe2 電子元件的研究群。結構上 MoTe2 材料是由上、下雙層 Te 原子以三明治結構方式夾擊 Mo 原子所形成之穩定系統,此外,由於 Te 原子相對於 Mo 原子鍵結轉角上的差異,其電學特徵又可區分為金屬性 (β 態 ) 與半導體性 (α 態 ),為了研究該材料對於電晶體與積體電路發展的潛力,因此筆者研究團隊僅專注於半導體性的 MoTe2 電子元件探索。α 態的 MoTe2 塊材具有1 eV 能隙大小的非直接半導體材料,隨著厚度由塊材降低至單層,其能隙大小變化不大,但會由非直接能隙轉為直接能隙半導體,有利於光電能量的轉換,這樣一個與傳統 Si 元素相近的能隙大小,相較於其他 TMDs 材料預期將有著更好的光吸收特徵。此外,在理論的預測 MoTe2 具有高的載子遷移率,使得快速二維電子元件的開發變的可行。不同載子極性的塊材研究成果也已經在 20 多年前被報導,用來實現基礎積體電路元件的 p-n 二極體。有鑑於此,筆者的研究團隊,利用化學氣相傳輸 (Chemical Vapor Transport) 的方式,實現 α 態的 MoTe2 塊材的合成,並且率先採用物理性膠帶撕貼技術完成全球首個二維層狀MoTe2 電子元件的製作與電學探索 [35]。

圖 4: 二維層狀 MoTe2 電晶體,a. 基礎電學量測、b. 氣體感測潛能開發、c. 邏輯電路開發 [35-38]。

圖 4 中筆者將過去五年關於研究二維 MoTe2 電子元件的具體成果簡單摘錄。2014 年春天,筆者研究團隊首先驗證了單層 MoTe2 材料能夠透過物理性手段,成功的鋪放於器件基板上,透過這件事情的驗證,我們揭露了單層至多層 MoTe2 電晶體的基本電學特徵 ( 如圖 4a 所示 ),這項工作中,MoTe2 展現了非典型的單極性電流 - 電壓轉換特徵,透過閘極正、負電壓的施加,該層狀電子元件無論單層或是多層皆呈現雙極性的傳輸特徵 ( 即單一電晶體簡單地透過電場的操作,就可以表現出電子或電洞主導的特徵 ),這樣特異型的表現使得積體電路的設計能變得更加簡便,並預期能夠實現更高元件密度堆疊的可能性。此外,透過不同金屬電極的替換,該二維層狀電子元件的載子遷移率變得可以操控,並且表徵出 10-3~102cm2/V-sec 範疇的大小,該載子遷移率的範圍雖然小於當今對商業產品的最低要求,但其僅透過置換電極材料而非元素摻雜手段,達成可調控的載子遷移率,著實為二維電子元件工程的改善,提供一條新穎的方法。二維材料具備了大的表面對體積比例,因此電子元件受到環境氛圍影響特別明顯,筆者藉由這樣的特徵進一步的觀察到,可以透過二維 MoTe2 電晶體的交流電學量測,實現微小訊號環境感測器的功能,如圖 4b 所示。另一方面,因二維材料具有極薄的器件通道厚度,雖可以有效克服短溝道效應的影響,但也因為先天性地限制了傳統半導體工藝「電子 / 電洞摻雜手段的施行」,因此思考如何有效地控制層狀 MoTe2 電子元件的載子濃度,進而改變電學特徵,實現省電的邏輯電路,一直是發展二維層狀電晶體應用上重要的探討議題。筆者基於對於二維層狀 MoTe2 電晶體基礎電學機制的深刻認知,進一步地開發了一個全新電子 / 電洞可操控、反覆式摻雜手法,並稱此為 Electrothermal Doping Processes。筆者團隊透過真空下施加一高電場於二維層狀MoTe2 通道上的手段,實現了元件電子的摻雜;另一方面,將電子摻雜後的二維電晶體曝氣於大氣環境中,這樣電子摻雜的元件會被進一步地反轉為電洞摻雜;這些電子 / 電洞摻雜過程歸因於二維材料表面與水 / 氧分子結合所致 ( 即高靈敏環境感測因素所致 )。該工作中,筆者除了能精密調控兩種載子極性電晶體外,更實現了積體電路中的反向器、反或閘(not or gate, NOR gate) 與反及閘 (not and gate, NAND gate) 等重要且基礎的元件功能,如圖4c 所示。

V. 結語與展望:

『半導體』、『二維』材料電子元件的發展,可以粗略地由 2011 年瑞士 A. Kis 團隊於頂尖奈米期刊 Nature Nanotechnology 發表單層 MoS2 電晶體開始界定起,時至今日該領域的探索爆量發展,筆者對於二維電子元件的研究與理解也僅是冰山一角,就筆者角度而言,距離使用二維電子元件,乃至發展積體電路並進入日常,尚有一段非常長的研究道路。

“The World is Flat: A Brief History of the Twenty-First Century is an international best-selling book by Thomas Friedman that analyzes globalization in the early 21st century. The title, perhaps modified to The world is 2D, is also appropriate for science in the 21st century, as exemplified by the recent interest in graphene and other two-dimensional (2D) materials” [39],這是一段摘錄於 2013 年 7 月頂級奈米領域期刊 ACS Nano 第七期第七卷第一頁雜誌中,編輯者引言所使用的開場白,說明了石墨烯與其相關二維材料的研究在近年所受到的高度重視;西元前三百三十年,古希臘哲學家亞里斯多德發現越往北走,北極星離地面漸高,而越往南行,卻看到北極星離地面越低,因此,根據經驗法則,他提出大地是球體的概念,然而這樣打破傳統思維的想法卻一直受到擁護大地平面說學者的批判,直到西元後一千五百年才由哥倫布證實大地球體說的正確性;2004 年證實石墨烯存在後,二十一世紀的科學家或工程師又將精力再次集中於這讓人熱血沸騰的二維世界中,筆者希望透過雙月刊這短短的物理專文撰寫機會,激發讀者內心對該領域未知探索的渴望,更進而參與其中、樂在其中。

參考資料:

1. J. Kilby, IEEE Trans. of Electron Devices 23, 648 (1976).

2. C. H. Museum, https://go.nature.com/2wF9Q1r (2018).

3. F. Schwierz, J. Pezoldt and R. Granzner, Nanoscale 7, 8261 (2015).

4. R. H. Yan, A. Ourmazd and K. F. Lee, IEEE Trans. Electron Devices 39, 1704 (1992).

5. H. Liu, A. T. Neal and P. D. Ye, ACS Nano 6, 8563 (2012).

6. S. M. Sze, Physics of Semiconductor Devices 1st edn., John Wiley (1969).

7. M. S. Lundstrom, Proc. IEEE Int. SOI Conf. 1-3 (2006).

8. P. L. McEuen, Nature 393, 15 (1998).

9. K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva and A. A. Firsov, Science 306, 666 (2004).

10. K. S. Novoselov and A. H. Castro Neto, Phys. Scr. T146, 014006 (2012).

11. A. K. Geim and I. V. Grigorieva, Nature 499, 419 (2013).

12. S. Wachter, D. K. Polyushkin, O. Bethge and T. Mueller, Nat. Commun. 8, 14948 (2017).

13. M. Chhowalla, H. S. Shin, G. Eda, L. J. Li, K. P. Loh, and H. Zhang, Nat. Chem. 5, 263 (2013).

14. H. Schmidt, F. Giustiniano, and G. Eda, Chem. Soc. Rev. 44, 7715 (2015).

15. B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti and A. Kis, Nat. Nanotechnol. 6, 147 (2011).

16. F. Wang, Z. Wang, C. Jiang, L. Yin, R. Cheng, X. Zhan, K. Xu, F. Wang, Y. Zhang, and J. He, small 13, 1604298 (2017).

17. C. R. Dean, A. F. Young, I. Meric, C. Lee, L. Wang, S. Sorgenfrei, K. Watanabe, T. Taniguchi, P. Kim, K. L. Shepard and J. Hone, Nat. Nanotehnol. 5, 722 (2010).

18. A. C. Ferrari, F. Bonaccorso, V. Fal'ko, K. S. Novoselov, S. Roche, P. Boggild, S. Borini, F. H. Koppens, V. Palermo, N. Pugno, J. A. Garrido, R. Sordan, A. Bianco, L. Ballerini, M. Prato, E. Lidorikis, J. Kivioja, C. Marinelli, T. Ryhanen, A. Morpurgo, J. N. Coleman,V. Nicolosi, L. Colombo, A. Fert, M. Garcia-Hernandez, A. Bachtold, G. F. Schneider, F. Guinea, C. Dekker, M. Barbone, Z. Sun, C. Galiotis, A. N. Grigorenko, G. Konstantatos, A. Kis, M. Katsnelson, L. Vandersypen, A. Loiseau, V. Morandi, D. Neumaier, E. Treossi, V.

Pellegrini, M. Polini, A. Tredicucci, G. M. Williams, B. H. Hong, J. H. Ahn, J. M. Kim, H. Zirath, B. J. van Wees, H. van der Zant, L. Occhipinti, A. Di Matteo, I. A. Kinloch, T. Seyller, E. Quesnel, X. Feng, K. Teo, N. Rupesinghe, P. Hakonen, S. R. Neil, Q. Tannock, T. Lofwander and J. Kinaret, Nanoscale 7, 4598 (2015).

19. K. Roy, M. Padmanabhan, S. Goswami, T. P. Sai, G. Ramalingam, S. Raghavan and A Ghosh, Nat. Nanotechnol. 8, 826 (2013).

20. T. Georgiou, R. Jalil, B. D. Belle, L. Britnell, R. V. Gorbachev, S. V. Morozov, Y. J. Kim, A. Gholinia, S. J. Haigh, O. Makarovsky, L. Eaves, L. A. Ponomarenko, A. K. Geim, K. S. Novoselov and A. Mishchenko, Nat. Nanotechnol. 8, 100 (2013).

21. W. J. Yu, Z. Li, H. Zhou, Y. Chen, Y. Wang, Y. Huang and X. Duan, Nat. Mater. 12, 246 (2013).

22. L. Britnell, R. V. Gorbachev, R. Jalil, B. D. Belle, F. Schedin, A. Mishchenko, T. Georgiou, M. I. Katsnelson, L. Eaves, S. V. Morozov, N. M. R. Peres, J. Leist, A. K. Geim, K. S. Novoselov and L. A. Ponomarenko, Science 335, 947 (2012).

23. M. S. Choi, G. H. Lee, Y. J. Yu, D. Y. Lee, S. H. Lee, P. Kim, J. Hone and W. J. Yoo, Nat. Commun. 4, 1624 (2013).

24. W. J. Yu, Y. Liu, H. Zhou, A. Yin, Z. Li, Y. Huang and X. Duan, Nat. Nanotechnol. 8, 952 (2013).

25. L. Britnell, R. M. Ribeiro, A. Eckmann, R. Jalil, B. D. Belle, A. Mishchenko, Y. J. Kim, R. V. Gorbachev, T. Georgiou, S. V. Morozov, A. N. Grigorenko, A. K. Geim, C. Casiraghi, A. H. C. Neto and K. S. Novoselov, Science 340, 1311 (2013).

26. K. Roy, M. Padmanabhan, S. Goswami, T. P. Sai, G. Ramalingam, S. Raghavan and A Ghosh, Nat. Nanotechnol. 8, 826 (2013).

27. T. Georgiou, R. Jalil, B. D. Belle, L. Britnell, R. V. Gorbachev, S. V. Morozov, Y. J. Kim, A. Gholinia, S. J. Haigh, O. Makarovsky, L. Eaves, L. A. Ponomarenko, A. K. Geim, K. S. Novoselov and A. Mishchenko, Nat. Nanotechnol. 8, 100 (2013).

28. W. J. Yu, Z. Li, H. Zhou, Y. Chen, Y. Wang, Y. Huang and X. Duan, Nat. Mater. 12, 246 (2013).

29. L. Britnell, R. V. Gorbachev, R. Jalil, B. D. Belle, F. Schedin, A. Mishchenko, T. Georgiou, M. I. Katsnelson, L. Eaves, S. V. Morozov, N. M. R. Peres, J. Leist, A. K. Geim, K. S. Novoselov and L. A. Ponomarenko, Science 335, 947 (2012).

30. M. S. Choi, G. H. Lee, Y. J. Yu, D. Y. Lee, S. H. Lee, P. Kim, J. Hone and W. J. Yoo, Nat. Commun. 4, 1624 (2013).

31. W. J. Yu, Y. Liu, H. Zhou, A. Yin, Z. Li, Y. Huang and X. Duan, Nat. Nanotechnol. 8, 952 (2013).

32. L. Britnell, R. M. Ribeiro, A. Eckmann, R. Jalil, B. D. Belle, A. Mishchenko, Y. J. Kim, R. V. Gorbachev, T. Georgiou, S. V. Morozov, A. N. Grigorenko, A. K. Geim, C. Casiraghi, A. H. C. Neto and K. S. Novoselov, Science 340, 1311 (2013).

33. J. Miao, Z. Xu, Q. Li, A. Bowman, S. Zhang, W. Hu, Z. Zhou, and C. Wang, ACS Nano 11, 10472 (2017).

34. R. M. A. Lieth, Preparation and crystal growth of materials with layered structures. Vol.1. Springer (1977).

35. Y. F. Lin, Y. Xu, S. T. Wang, S. L. Li, M. Yamamoto, A. A. Ferreira, W. Li, H. Sun, W. B. Jian, S. Nakaharai, K. Ueno and K. Tsukagoshi, Adv. Mater. 26, 3263 (2014).

36. Y. F. Lin, Y. Xu, C. Y. Lin, Y. W. Suen, M. Yamamoto, S. Nakaharai, K. Ueno, and K. Tsukagoshi, Adv. Mater.

27, 6612 (2015).

37. Y. M. Chang, C. Y. Lin, Y. F. Lin, and K. Tsukagoshi, Jpn. J. Appl. Phys. 55, 1102A1 (2016).

38. Y. M. Chang, S. H. Yang, C. Y. Lin, C. H. Chen, C. H. Lien, W. B. Jian, K. Ueno, Y. W. Suen, K. Tsukagoshi, and Y. F. Lin, Adv. Mater. 30, 1706995 (2018).

39. A. T. S. Wee, ACS Nano 7, 5649 (2013).